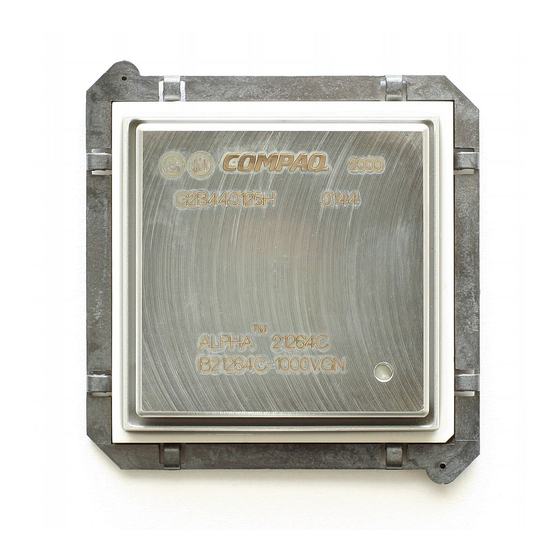

Compaq 21264 Manuals

Manuals and User Guides for Compaq 21264. We have 2 Compaq 21264 manuals available for free PDF download: Hardware Reference Manual

Compaq 21264 Hardware Reference Manual (356 pages)

Compaq Microprocessor Reference Manual

Brand: Compaq

|

Category: Computer Hardware

|

Size: 4.18 MB

Table of Contents

-

-

-

-

Replay Traps59

-

-

-

-

-

Page Hit Mode108

-

-

-

Sysfillvalid_L123

-

Data Wrapping124

-

-

-

Bcache Port Pins131

-

-

-

-

-

-

Status Flags196

-

-

Mf_Fpcr196

-

Mt_Fpcr196

-

-

ITB Fill200

-

-

-

Operation203

-

-

-

Operation205

-

-

CMOV Decomposed205

-

-

-

Fault Reset Flow216

-

-

-

Warm Reset Flow219

-

Advertisement

Compaq 21264 Hardware Reference Manual (356 pages)

Compaq Microprocessor Reference Manual

Brand: Compaq

|

Category: Computer Hardware

|

Size: 4.31 MB

Table of Contents

-

-

-

-

Data Cache40

-

-

-

-

Page Hit Mode108

-

-

-

Sysfillvalid_L123

-

Data Wrapping124

-

-

-

Bcache Port Pins131

-

-

-

-

-

Status Flags196

-

Mf_Fpcr196

-

Mt_Fpcr196

-

-

ITB Fill200

-

-

-

Operation203

-

-

-

Operation205

-

-

CMOV Decomposed205

-

-

-

Fault Reset Flow216

-

-

-

Warm Reset Flow219

-

Advertisement

Related Products

- Compaq 210189-001 - P 710 - 17" CRT Display

- Compaq 215999-002 - Deskpro EX - 64 MB RAM

- Compaq 219700-001 - ProLiant - 1500

- Compaq 2140 - Mini-Note - Atom 1.6 GHz

- Compaq StorageWorks 2/12 - Edge Switch

- Compaq Presario 2100 - Desktop PC

- Compaq 215487-B21 - StorageWorks AIT 50 GB Tape Drive

- Compaq 216886-B21 - StorageWorks AIT 35 GB Tape Drive

- Compaq 219700-001 1500

- Compaq 2010c